BUCK电路中自举式电源的分析

BUCK电路中自举式电源的是一种应用较为广泛的,给高端栅极MOS驱动IC供电的方法。这种自举式电源的技术简单,且成本低。但是他的缺点是受到自举式电容的刷新速率的影响会限制了占空比。

一、举例分析

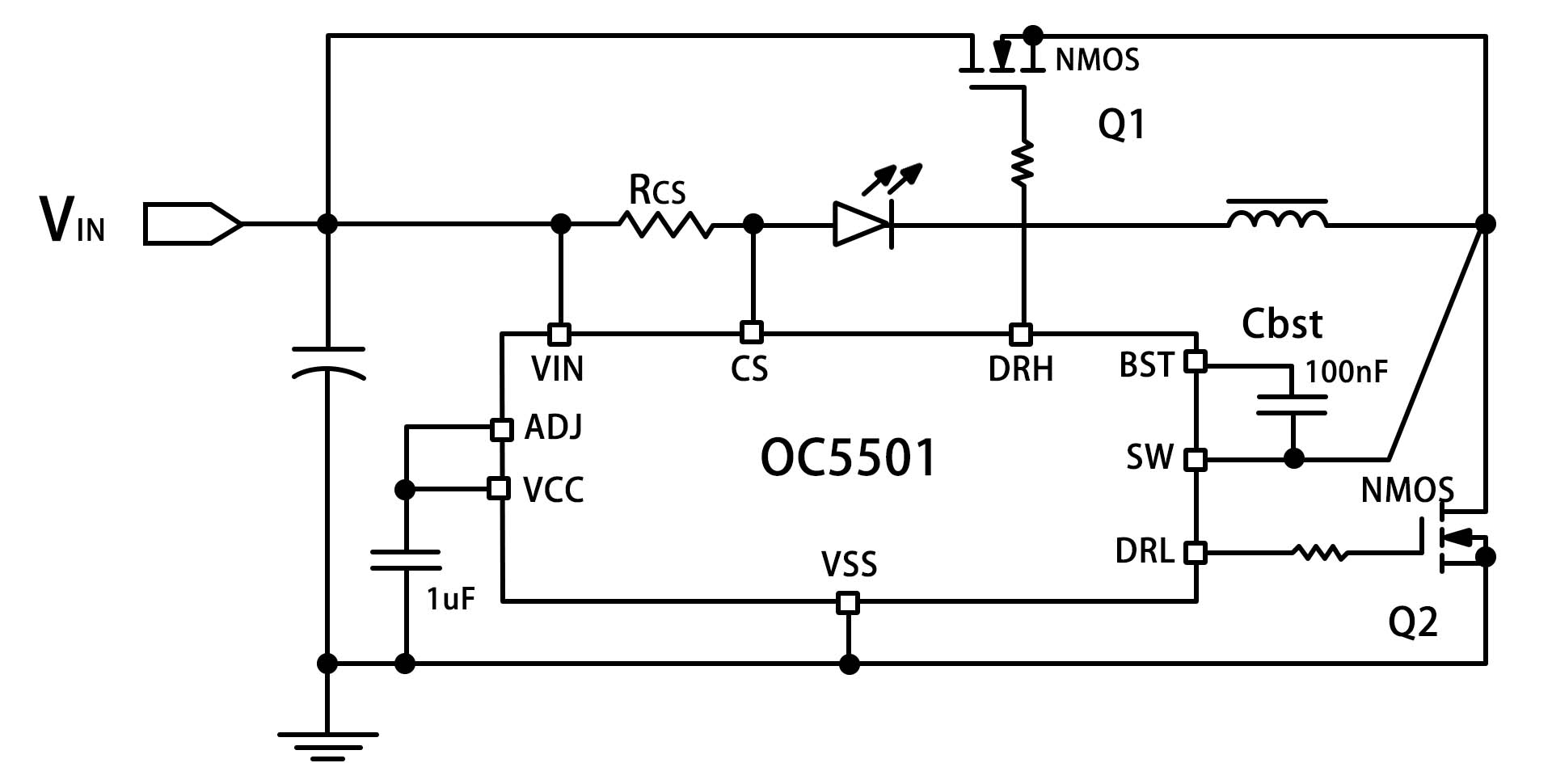

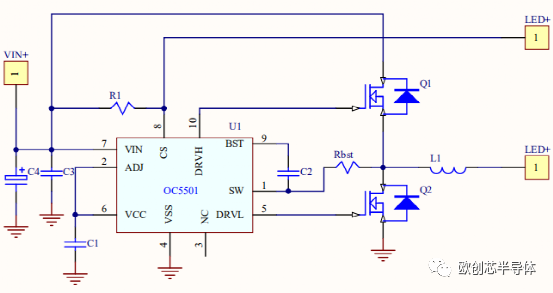

以我司的OC5501同步DC-DC降压恒流芯片中自举电容CBST电容分析,OC5501的电路接线原理图如下:

1、分析我司同步DC-DC恒流芯片的MOS管状态

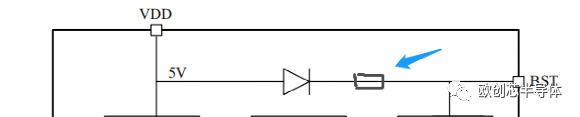

在下管Q2导通时,SW管脚电压在是接GND的,自举电容此刻由VDD经二极管进行充电,电压值会变为VDD-VD;VD为二极管的压降。

在下管Q2断开时,SW由GND变为Vin,内部二极管处于反向偏置状态,自举电容两端的电压不能突变,因此BST端的对地电压变为Vin+VDD-VD,我们都知道NMOS的导通条件必须是栅源电压VGS高于MOS的门限电压VGS(TH),这样就可以通过驱动器使上NMOS的VGS电压达到了VDD值,即为5.0V-0.4V=4.6V,进而可以驱动上管MOS/Q1导通。

2、CBST电容的耐压和容量选择

从上面的理论分析结果可知,CBST电容两端电压为VDD电压,即为5V,我们也可从产品的规格书上可知,BST对SW电压值为7V,那么常规CBST电容的耐压可选择10V,16V等常规耐压值,由于NMOS为电压低压功率器件,Qg值不大,需要的电流很小,仅给MOS结电容充电即可,同时自举电容也常规用贴片陶瓷电容,漏电流小。所以常规CBST电容的容量选择使用100nF。

二、什么时候需要自举电路

在直驱式的电路中,不会出现BST引脚和外接的BST电容。

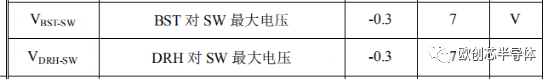

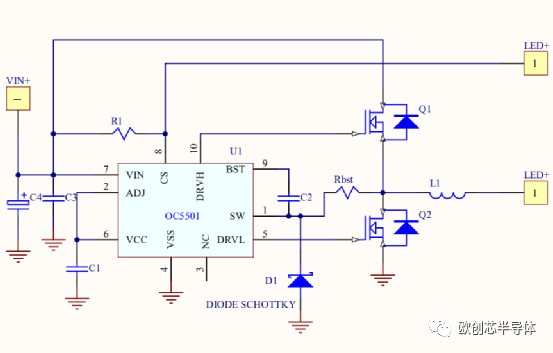

如下图所示异步的降压电路中,上管驱动为P-MOS,下管为肖特基二极管,以我司的OC5820系列为例,外围就会省去CBST电容。

三、自举电路的缺点

自举电路的占空比和导通时间受BST电容的充放电速度影响。

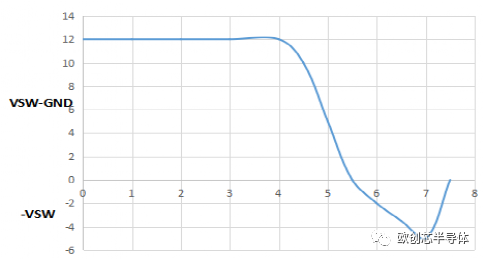

此电路还有个大问题在于:在上管关闭的时候,其源极的负压会使负载的电流通过到下管MOS的续流二极管,如图下所示。

负压的产生是走线上或者芯片内部线路的寄生电感产生。计算式,这里假定12V驱动5A的输出电流,寄生电感的参数为50nH,如果要在50nS内开关,那么VSW与地的负电压尖峰值可达到-5V。负压的幅度和寄生电感、di/dt成正比,其中开关速度和MOS栅极电阻和MOS的输入电容Ciss参数有关。

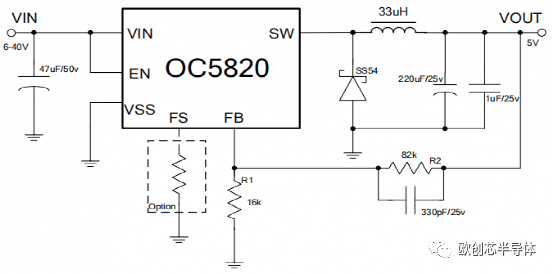

同时负压的存在,会导致BST对SW的电压,即BST电容两端电压超过了耐压值。

BST电容两端的电压VCBST=VDD-VD-(-VSW)

该负压会带来一个问题,SW脚是直接和芯片的引脚连接的,可能会将芯片内部的某些电路拉到地以下,导致芯片出现不可逆的损坏,或者导致芯片处于闭锁状态,无法正常驱动。

四、自举电路的几种参考设计

1、在自举二极管上串联一个小电阻,此电阻仅在充电周期内起到限流作用,但是此电阻不能太大,一般选择5-10欧之间,太大会影响启动时间。

2、在SW到电感之间串联一个小电阻Rbst,此电阻作用于充电周期和放电周期内,此电阻阻值选择一般也是5-10欧之间。

3、在增加一个反向的肖特基二极管D1。

深圳市程华电子有限公司主营产品包括中低压MOS管、DC-DC恒流IC、DC-DC恒压IC和肖特基二极管等。

服务与支持:深圳市程华电子有限公司为客户提供产品选型、样板测试、技术支持等一体服务,可根据客户的参数要求提供高质量的芯片、成熟可靠的芯片解决方案、MOS管芯片订制、免费样品和DEMO板测试等。

QQ客服

QQ客服